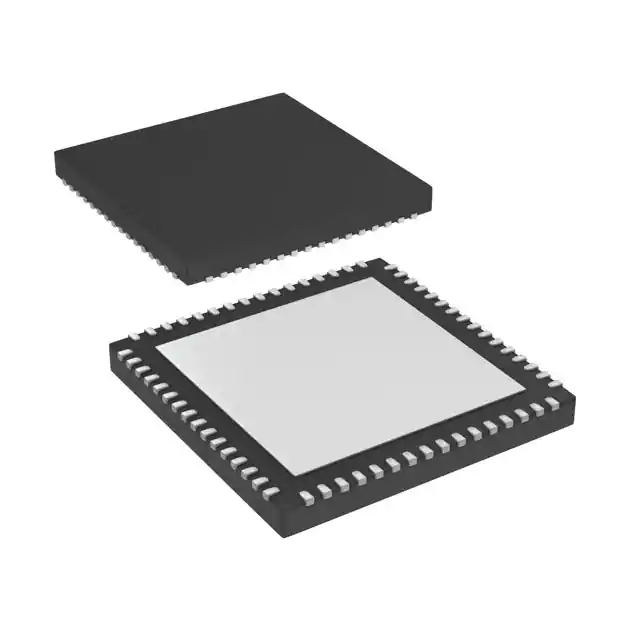

DS90UB936TRGZTQ1 S VQFN-64 UB947Q インターフェース IC チップ

製品の属性

| タイプ | 説明 |

| カテゴリー | 集積回路 (IC) |

| インターフェイス - シリアライザー、デシリアライザー | |

| 製造元 | テキサス・インスツルメンツ |

| シリーズ | 自動車、AEC-Q100 |

| パッケージ | テープ&リール(TR) |

| カットテープ(CT) | |

| 部品のステータス | アクティブ |

| 関数 | シリアライザー |

| データレート | 3.36Gbps |

| 入力方式 | LVDS |

| 出力タイプ | FPD-Link III、LVDS |

| 入力数 | 8 |

| 出力数 | 2 |

| 電圧 - 電源 | 1.71V~1.89V |

| 動作温度 | 氷点下40℃~105℃(TJ) |

| 取付タイプ | 表面実装 |

| パッケージ・ケース | 64-VFQFN 露出パッド |

| サプライヤーデバイスパッケージ | 64-VQFN (9x9) |

| 基本製品番号 | DS90UB947 |

集積回路タイプ

シリアル変換、パラレル変換などの情報形式の変換。

CPUS とペリフェラル間の情報の種類とレベルの違いを調整する機能。たとえば、水平変換ドライバ、d/A または A/D コンバータなど。

時間的な違いを調整する

アドレスデコードおよび選択機能

割り込みおよび DMA 要求信号が DMA 許可で生成され、割り込みおよび DMA 応答が受け付けられた後に割り込み処理および DMA 転送が完了するように、割り込みおよび DMA 制御ロジックを設定します。

入出力インターフェイスは、特殊なレジスタと対応する制御論理回路で構成される電子回路で、通常は IC チップまたはインターフェイス ボードです。CPU と入出力デバイス間の情報交換の媒体およびブリッジです。CPUと外部デバイス間の接続、メモリとデータ交換はインターフェースデバイスを介して完了する必要があり、前者はI/Oインターフェースと呼ばれ、後者はメモリインターフェースと呼ばれます。メモリは一般にCPUによる同期制御であり、インターフェース回路は比較的単純です。I/O デバイスの種類に応じてインターフェイス回路が異なるため、インターフェイスは従来 I/O インターフェイスと呼ばれています。主に以下のI/Oインターフェースハードウェアがあります。

シリコンベースのフォトニックデバイスとCMOS回路には2つの集積方法があります。

前者の利点は、光デバイスと電子デバイスを個別に最適化できることですが、その後のパッケージングが難しく、商業用途が制限されることです。後者は、2 つのデバイスの設計と統合プロセスが困難です。現時点では、核粒子統合に基づくハイブリッドアセンブリが最良の選択です

例1.入出力インターフェースチップ

ほとんどのチップは集積回路であり、CPU を介してさまざまな命令とパラメータを入力し、対応する動作のために関連する I/O 回路と単純な外部デバイスを制御します。一般的なインターフェイス チップには、タイミング/カウンタ、割り込みコントローラ、DMA コントローラ、パラレル インターフェイスなどがあります。の上。

例 2. 入出力インターフェース制御カード

ロジックによっては、複数の集積回路が 1 つの部品となり、CPU に直接接続されるか、プラグインがシステムのスロットに挿入される場合があります。

.png)