-

DP83848CVVX/NOPB オリジナル電子部品 IC チップ集積回路

PHY チップはアナログとデジタルのハイブリッド回路であり、電気や光などのアナログ信号の受信を担当します。復調と A/D 変換の後、信号は MAC チップに送信され、MII インターフェイスを介して処理されます。一般に、MAC チップは純粋なデジタル回路です。物理層は、データの送受信に必要な電気信号と光信号、回線ステータス、クロック基準、データエンコーディングおよび回路を定義し、データリンク層デバイスに標準インターフェイスを提供します。物理層チップはPHYと呼ばれます。

-

TPA3128D2DAPR 新しい & オリジナル DC/DC コンバータ & スイッチングレギュレータチップ

TPA3128D2 クラス D アンプは、アイドル時の電力損失が低くなります。この機能は、Bluetooth/ワイヤレス スピーカーやその他のバッテリー駆動のオーディオ システムのバッテリー寿命を延ばすのに役立ちます。TPA3128D2 デバイスは非常に効率が高く、2 層 PCB 上に外部ヒートシンクを必要とせずに 2 × 30W を供給できます。TPA3128D2 の高度な発振器/プログラマブル フェーズ ロック ループ (PLL) 回路は、複数のスイッチング周波数オプションを備えています。このオプションを使用すると、デバイスは AM 干渉を回避でき、マスター/スレーブ モード オプションと併用すると、複数のデバイスを同期できるようになります。

-

LMR14030SQDDARQ1 オリジナルと新しい、競争力のある価格で在庫 IC サプライヤー

レギュレータの幅広い調整可能なスイッチング周波数範囲により、効率や外部部品のサイズを最適化できます。内部ループ補償は、ユーザーがループ補償コンポーネントを設計するという面倒な作業を行う必要がないことを意味します。また、デバイスの外部コンポーネントの数を最小限に抑えることもできます。高精度のイネーブル入力により、レギュレータ制御とシステム電源シーケンスが簡素化されます。さらに、このデバイスには、サイクルごとの電流制限保護、過度の電力消費に対する温度センシングおよびサーマルシャットダウン保護、出力過電圧保護など、いくつかの保護機能が組み込まれています。

-

AM1808EZWT3 オリジナルと新しい、競争力のある価格で在庫 IC サプライヤー

マイコンチップは、制御プログラムを記述することでモーターや照明、センサーなどの制御をはじめ、タイマーやカウンタ、割り込み処理などの機能を実装し、回路の制御や動作を実現します。

-

OPA1612AIDR 高性能バイポーラ入力オーディオオペアンプ

OPA1612AIDR 汎用アンプは、オーディオ増幅技術の最高峰です。その比類のない多用途性、パフォーマンス、信頼性により、あらゆるオーディオ アプリケーションにとって優れた選択肢となります。オーディオ業界のプロフェッショナルであろうと、究極のサウンド体験を求める単なるオーディオファンであろうと、このアンプは必需品です。今すぐオーディオ セットアップをアップグレードし、OPA1612AIDR ユニバーサル アンプでサウンド システムの真の可能性を解き放ちます。

-

組み込みおよび DSP-TMS320C6746EZWTD4

TMS320C6746 固定小数点および浮動小数点 DSP は、C674x DSP コアをベースとした低電力アプリケーション プロセッサです。この DSP は、TMS320C6000™ プラットフォームの他の DSP よりも消費電力が大幅に低くなります。

このデバイスにより、相手先ブランド供給メーカー (OEM) およびオリジナル設計メーカー (ODM) は、完全に統合された混合プロセッサ ソリューションの最大限の柔軟性を通じて、堅牢なオペレーティング システム、豊富なユーザー インターフェイス、および高いプロセッサ パフォーマンスを備えたデバイスを迅速に市場に投入できるようになります。デバイス DSP コアは 2 レベルのキャッシュベースのアーキテクチャを使用します。レベル 1 プログラム キャッシュ (L1P) は 32 KB のダイレクト マップ キャッシュで、レベル 1 データ キャッシュ (L1D) は 32 KB の 2 ウェイ、セットアソシアティブ キャッシュです。レベル 2 プログラム キャッシュ (L2P) は、プログラムとデータ空間の間で共有される 256 KB のメモリ空間で構成されます。L2 メモリは、マップされたメモリ、キャッシュ、またはその 2 つの組み合わせとして構成できます。DSP L2 は、システム内の他のホストからアクセスできます。 -

ロジックおよびフリップフロップ-SN74LVC74APWR

SNx4LVC74A デバイスは、2 つのポジティブエッジ トリガ D タイプ フリップフロップを 1 つの便利なデバイスに統合しています。

デバイス。

SN54LVC74A は 2.7 V ~ 3.6 V の VCC 動作向けに設計されており、SN74LVC74A は

1.65V ~ 3.6V の VCC で動作。プリセット (PRE) またはクリア (CLR) 入力の Low レベルは、他の入力のレベルに関係なく、出力をセットまたはリセットします。PRE と CLR が非アクティブ (High) の場合、セットアップ時間要件を満たすデータ (D) 入力のデータは、クロック パルスの立ち上がりエッジで出力に転送されます。クロックのトリガは電圧レベルで発生し、クロック パルスの立ち上がり時間には直接関係しません。ホールド時間間隔の後、出力のレベルに影響を与えることなく、D 入力のデータを変更できます。データ I/O と制御入力は過電圧耐性があります。この機能により、混合電圧環境でのダウントランスレーションにこれらのデバイスを使用できるようになります。 -

リアルタイムクロック - PCF8563T/F4,118

PCF8563 は、低消費電力向けに最適化された CMOS1 リアルタイム クロック (RTC) およびカレンダーです消費。プログラム可能なクロック出力、割り込み出力、および低電圧検出器が備わっています。も提供されます。すべてのアドレスとデータは 2 線の双方向経由でシリアル転送されます。I 2Cバス。最大バス速度は 400 kbit/s です。レジスタアドレスがインクリメントされます各データバイトの書き込みまたは読み取り後に自動的に実行されます。 -

TPS62136RGXR – 電圧レギュレータ、DC DC スイッチングレギュレータ

TPS62136 および TPS621361 は高効率です

使いやすい同期降圧DC-DC

DCS-Control™ トポロジに基づくコンバータ。

このデバイスは 3V ~ 17V の広い入力電圧範囲に対応します

マルチセルのリチウムイオンおよび 12 V に適しています。

中間電源レール。デバイスは 4-A を提供します

連続出力電流。TPS62136

軽負荷時には自動的に省電力モードに移行します

負荷全体にわたって高い効率を維持するため

範囲。そのため、このデバイスは次のような用途に適しています。

コネクトスタンバイを必要とするアプリケーション

超低電力コンピュータのようなパフォーマンス。とともに

MODE ピンを Low に設定すると、スイッチング周波数が低くなります。

デバイスは入力に基づいて自動的に適応されます

そして出力電圧。 -

LCMXO2-256HC-4TG100C オリジナルおよび新しい、競争力のある価格の在庫 IC サプライヤー

Complex Programmable Logic Device (CPLD) は、LSI (Large Scale Integrated Circuit) 集積回路内の特定用途向け集積回路 (ASIC) です。制御重視のデジタルシステム設計に適しており、遅延制御も便利です。CPLD は、集積回路において最も急速に成長しているデバイスの 1 つです。

CPLDのコンポーネント

CPLD は、大規模かつ複雑な構造を備えた複雑なプログラマブル ロジック デバイスであり、大規模集積回路の範囲に属します。 -

TPA2013D1RGPR オーディオアンプスピーカー電子部品集積回路 IC チップ 100% 新しい & オリジナル

このTPA2013D1RGPRクラスDアンプは広い中帯域を持っています。このオーディオアンプは最大 1700 mA の電流を処理できます。最大消費電力は 2500 mW です。差動入力信号と差動出力信号を備えています。最大負荷抵抗は8オームです。標準的なデュアル電源電圧は 3|5 V、最小 1.8|3 V、最大 5.5 V です。1 チャンネルのモノラル出力を備えています。このオーディオアンプの最低動作温度は -40 °C、最高 85 °C です。このデバイスは二重電源を使用します。

-

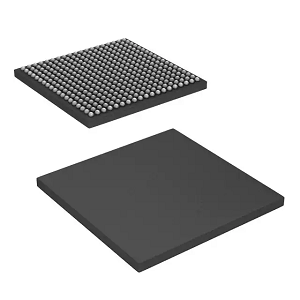

XCKU060-1FFVA1156I オリジナル新最高価格在庫 IC サプライヤー

製品属性 タイプ 説明 カテゴリ 集積回路 (IC) 組み込み FPGA (フィールド プログラマブル ゲート アレイ) 製造元 AMD シリーズ Kintex® UltraScale™ パッケージ バルク製品ステータス アクティブな LAB/CLB の数 41460 ロジック エレメント/セルの数 725550 合計 RAM ビット 38912000 I の数/O 520 電圧 – 供給 0.922V ~ 0.979V 実装タイプ 表面実装 動作温度 -40°C ~ 100°C (TJ) パッケージ/ケース 1156-BBGA、FCBGA サプライヤー デバイス パッケージ 1156-FCBG...