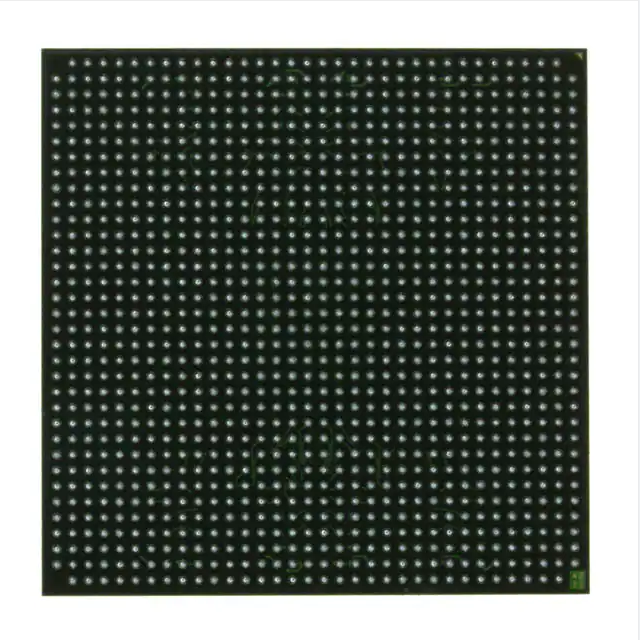

SEESEND オリジナルおよび新しい集積回路電子部品 XC2VP50-6FF1152I

製品の属性

| タイプ | 説明 |

| カテゴリー | 集積回路 (IC) |

| 製造元 | AMDザイリンクス |

| シリーズ | Virtex®-II プロ |

| パッケージ | トレイ |

| 製品の状態 | 廃止 |

| LAB/CLB の数 | 5904 |

| ロジックエレメント/セルの数 | 53136 |

| 合計RAMビット数 | 4276224 |

| I/O数 | 692 |

| 電圧 – 電源 | 1.425V~1.575V |

| 取付タイプ | 表面実装 |

| 動作温度 | -40℃~100℃(TJ) |

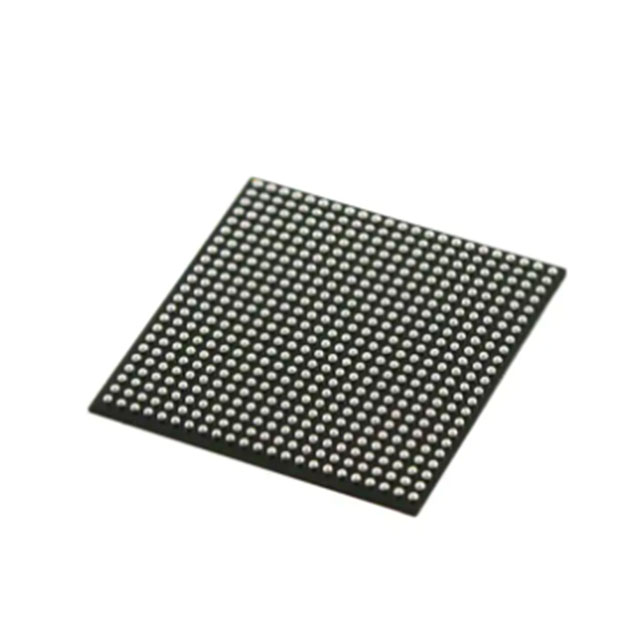

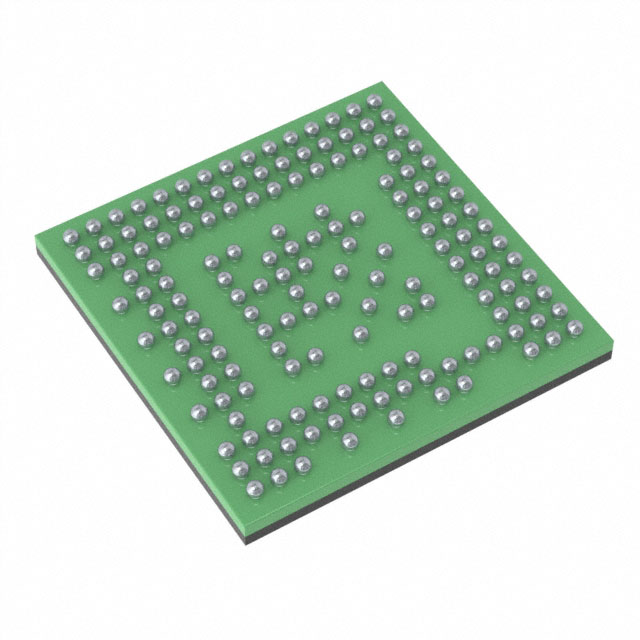

| パッケージ・ケース | 1152-BBGA、FCBGA |

| サプライヤーデバイスパッケージ | 1152-FCBGA (35×35) |

| 基本製品番号 | XC2VP50 |

文書とメディア

| リソースの種類 | リンク |

| データシート | Virtex-II プロ、プロ X |

| 環境情報 | ザイリンクス RoHS 認証 |

| PCN の廃止/EOL | Mult 開発 EOL 6/Jan/2020 |

| HTML データシート | Virtex-II プロ、プロ X |

| EDAモデル | XC2VP50-6FF1152I (Ultra Librarian 著) |

環境および輸出の分類

| 属性 | 説明 |

| RoHS ステータス | RoHS非対応 |

| 感湿性レベル (MSL) | 4 (72時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

XC2VP50-6FF1152I FPGA の概要

Virtex-II Pro および Virtex-II Pro X ファミリには、IP コアおよびカスタマイズされたモジュールに基づくデザイン用のプラットフォーム FPGA が含まれています。XC2VP50-6FF1152I には、Virtex-II Pro シリーズ FPGA アーキテクチャにマルチギガビット トランシーバーと PowerPC CPU ブロックが組み込まれています。通信、ワイヤレス、ネットワーキング、ビデオ、DSP アプリケーションの完全なソリューションを実現します。

最先端の 0.13 µm CMOS 9 層銅プロセスと Virtex-II Pro アーキテクチャは、幅広い密度での高性能デザイン向けに最適化されています。XC2VP50-6FF1152I は、さまざまな柔軟な機能と IP コアを組み合わせてプログラマブル ロジック設計機能を強化し、マスク プログラムされたゲート アレイの強力な代替品となります。

ザイリンクスの産業用コンポーネント シリーズ XC2VP50-6FF1152I は、53136 ロジック セル、16 ロケット IO 2 電源、データシート、在庫、認定代理店の価格とともに FPGAkey.com で代替品と代替品を表示します。また、他の FPGA 製品を検索することもできます。

特徴

高性能プラットフォーム FPGA ソリューション (以下を含む)

最大 20 個の RocketIO または RocketIO X 組み込みマルチギガビット トランシーバー (MGT)

最大 2 つの IBM PowerPC RISC プロセッサ ブロック

Virtex-II プラットフォーム FPGA テクノロジに基づく

柔軟なロジックリソース

SRAMベースのインシステム構成

アクティブインターコネクトテクノロジー

SelectRAM+ メモリ階層

専用の 18 ビット x 18 ビット乗算器ブロック

高性能クロック管理回路

SelectI/O-Ultra テクノロジー

XCITE デジタル制御インピーダンス (DCI) I/O