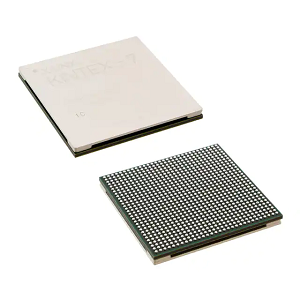

XC7K420T-2FFG901I – 集積回路、組み込み、フィールド プログラマブル ゲート アレイ

製品の属性

| タイプ | イラストレーションする |

| カテゴリー | 集積回路 (IC)埋め込み フィールド プログラマブル ゲート アレイ (FPGA) |

| メーカー | AMD |

| シリーズ | Kintex®-7 |

| 包む | トレイ |

| 商品の状態 | アクティブ |

| DigiKey はプログラム可能です | 検証されていない |

| LAB/CLB番号 | 32575 |

| 論理エレメント数/ユニット数 | 416960 |

| RAMビットの総数 | 30781440 |

| I/O数 | 380 |

| 電圧 - 電源 | 0.97V~1.03V |

| 設置タイプ | 表面粘着タイプ |

| 動作温度 | -40℃~100℃(TJ) |

| パッケージ/ハウジング | 900-BBGA、FCBGA |

| ベンダーコンポーネントのカプセル化 | 901-FCBGA (31x31) |

| 製品マスター番号 | XC7K420 |

| タイプ | イラストレーションする |

| カテゴリー | 集積回路 (IC)埋め込み |

| メーカー | AMD |

| シリーズ | Kintex®-7 |

| 包む | トレイ |

| 商品の状態 | アクティブ |

| DigiKey はプログラム可能です | 検証されていない |

| LAB/CLB番号 | 32575 |

| 論理エレメント数/ユニット数 | 416960 |

| RAMビットの総数 | 30781440 |

| I/O数 | 380 |

| 電圧 - 電源 | 0.97V~1.03V |

| 設置タイプ | 表面粘着タイプ |

| 動作温度 | -40℃~100℃(TJ) |

| パッケージ/ハウジング | 900-BBGA、FCBGA |

| ベンダーコンポーネントのカプセル化 | 901-FCBGA (31x31) |

| 製品マスター番号 | XC7K420 |

FPGA

利点

FPGA の利点は次のとおりです。

(1) FPGA は、論理セル、RAM、乗算器などのハードウェア資源から構成されます。これらのハードウェア資源を合理的に構成することで、乗算器、レジスタ、アドレス生成器などのハードウェア回路を実装できます。

(2) FPGA は、単純なゲート回路から FIR または FFT 回路まで、ブロック図または Verilog HDL を使用して設計できます。

(3) FPGA は無限に再プログラムでき、再コンフィギュレーションを使用してハードウェアのオーバーヘッドを削減し、わずか数百ミリ秒で新しい設計ソリューションをロードできます。

(4) FPGA の動作周波数は、設計だけでなく FPGA チップによっても決定され、特定の厳しい要件を満たすために変更したり、より高速なチップに置き換えたりすることができます (ただし、もちろん、動作周波数は無制限ではなく、変更することもできます)。増加する可能性がありますが、現在の IC プロセスおよびその他の要因によって決まります)。

短所

FPGA の欠点は次のとおりです。

(1) FPGA はすべての機能をハードウェア実装に依存しており、条件付きジャンプの分岐などの操作を実装できません。

(2) FPGA は固定小数点演算のみを実装できます。

要約: FPGA はすべての機能を実装するためにハードウェアに依存しており、速度の点では専用チップと比較できますが、汎用プロセッサと比較すると設計の柔軟性には大きなギャップがあります。

デザイン言語とプラットフォーム

プログラマブル ロジック デバイスは、EDA テクノロジを通じて電子アプリケーションの確立された機能と技術仕様を具体化するハードウェア キャリアです。このパスを実装する主流デバイスの 1 つである FPGA は、直接ユーザー指向であり、非常に柔軟で多用途で、使いやすく、テストやハードウェアへの実装が迅速に行えます。

ハードウェア記述言語 (HDL) は、デジタル ロジック システムを設計し、デジタル回路を記述するために使用される言語です。一般的に使用される主な言語は、VHDL、Verilog HDL、System Verilog、および System C です。

超高速集積回路ハードウェア記述言語 (VHDL) は、万能のハードウェア記述言語として、特定のハードウェア回路から独立し、設計プラットフォームからも独立しているという特徴を持ち、広範な記述機能という利点を備えています。特定のデバイスに依存する機能や、複雑な制御ロジックの設計を厳密かつ簡潔なコードで記述する機能など。多くの EDA 企業に支持され、電子設計の分野で広く使用されています。広く使われています。

VHDL は回路設計用の高級言語であり、他のハードウェア記述言語と比較して、単純な言語、柔軟性、デバイス設計からの独立性という特徴を備えており、EDA テクノロジーの共通ハードウェア記述言語となり、EDA テクノロジーをより高度なものにします。デザイナーがアクセスできるようになります。

Verilog HDL は、モデリング、合成、シミュレーションなどのハードウェア設計プロセスの複数の段階で使用できる、広く使用されているハードウェア記述言語です。

Verilog HDL の利点: C に似ており、習得が容易で柔軟性があります。大文字と小文字を区別。刺激とモデリングを書く上での利点。欠点: 多くのエラーはコンパイル時に検出できません。

VHDL の長所: 厳密な構文、明確な階層。短所: 慣れるまでに長い時間がかかり、十分な柔軟性がありません。

Quartus_II ソフトウェアは、アルテラが開発した完全なマルチプラットフォーム設計環境であり、さまざまな FPGA および CPLD の設計ニーズを満たすことができ、オンチップ プログラマブル システム設計のための包括的な環境です。

Vivado Design Suite は、FPGA ベンダーのザイリンクスが 2012 年にリリースした統合設計環境です。これには、高度に統合された設計環境と、システムから IC レベルに至る新世代のツールが含まれており、すべて共有されたスケーラブルなデータ モデルと共通のデバッグ環境に基づいて構築されています。Xilinx Vivado Design Suite は、デザインに簡単に適用できる FIFO IP コアを提供します。