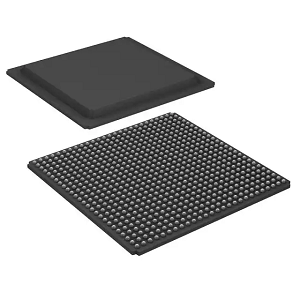

XC7Z030-2FFG676I – 集積回路 (IC)、組み込み、システム オン チップ (SoC)

製品の属性

| タイプ | 説明 |

| カテゴリー | 集積回路 (IC) |

| 製造元 | AMD |

| シリーズ | Zynq®-7000 |

| パッケージ | トレイ |

| 製品の状態 | アクティブ |

| 建築 | MCU、FPGA |

| コアプロセッサ | CoreSight™ を備えたデュアル ARM® Cortex®-A9 MPCore™ |

| フラッシュサイズ | - |

| RAM サイズ | 256KB |

| 周辺機器 | DMA |

| 接続性 | CANbus、EBI/EMI、イーサネット、I²C、MMC/SD/SDIO、SPI、UART/USART、USB OTG |

| スピード | 800MHz |

| 主な属性 | Kintex™-7 FPGA、125K ロジック セル |

| 動作温度 | -40℃~100℃(TJ) |

| パッケージ・ケース | 676-BBGA、FCBGA |

| サプライヤーデバイスパッケージ | 676-FCBGA (27x27) |

| I/O数 | 130 |

| 基本製品番号 | XC7Z030 |

文書とメディア

| リソースの種類 | リンク |

| データシート | Zynq-7000 オール プログラマブル SoC の概要 |

| 製品トレーニング モジュール | TI 電源管理ソリューションによるシリーズ 7 ザイリンクス FPGA への電力供給 |

| 環境情報 | ザイリンクス RoHS 認証 |

| 注目の製品 | すべてプログラム可能な Zynq®-7000 SoC |

| PCNの設計・仕様 | Mult 開発資料変更 16/Dec/2019 |

| 正誤表 | Zynq-7000 エラッタ |

環境および輸出の分類

| 属性 | 説明 |

| RoHS ステータス | ROHS3準拠 |

| 感湿性レベル (MSL) | 4 (72時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

アプリケーションプロセッサユニット(APU)

APU の主な機能は次のとおりです。

• デュアルコアまたはシングルコア ARM Cortex-A9 MPCore。各コアに関連する機能は次のとおりです。

• 2.5 DMIPS/MHz

• 動作周波数範囲:

- Z-7007S/Z-7012S/Z-7014S (ワイヤーボンド): 最大 667 MHz (-1);766MHz (-2)

- Z-7010/Z-7015/Z-7020 (ワイヤーボンド): 最大 667 MHz (-1);766MHz (-2);866MHz (-3)

- Z-7030/Z-7035/Z-7045 (フリップチップ): 667 MHz (-1);800MHz (-2);1GHz (-3)

- Z-7100 (フリップチップ): 667 MHz (-1);800MHz(-2)

• シングルプロセッサ、対称デュアルプロセッサ、および非対称デュアルプロセッサモードで動作する機能

• 単精度および倍精度浮動小数点: それぞれ最大 2.0 MFLOPS/MHz

• SIMD サポート用の NEON メディア処理エンジン

• コード圧縮のための Thumb®-2 サポート

• レベル 1 キャッシュ (個別の命令とデータ、それぞれ 32 KB)

- 4ウェイセットアソシアティブ

- それぞれ最大 4 つの未処理の読み取りミスと書き込みミスをサポートするノンブロッキング データ キャッシュ

• 統合メモリ管理ユニット (MMU)

• TrustZone® によるセキュアモード動作

• アクセラレータ コヒーレンシ ポート (ACP) インターフェイスにより、PL から CPU メモリ空間へのコヒーレント アクセスが可能になります。

• 統合レベル 2 キャッシュ (512 KB)

• 8ウェイセットアソシアティブ

• TrustZone を有効にして安全な操作を実現

• デュアルポート、オンチップ RAM (256 KB)

• CPU およびプログラマブル ロジック (PL) からアクセス可能

• CPU からの低遅延アクセス向けに設計

• 8チャンネルDMA

• 複数の転送タイプをサポート: メモリからメモリ、メモリからペリフェラル、ペリフェラルからメモリ、およびスキャッタギャザ

• 64 ビット AXI インターフェイスにより、高スループットの DMA 転送が可能

• PL専用の4チャンネル

• TrustZone を有効にして安全な操作を実現

• デュアル レジスタ アクセス インターフェイスにより、セキュア アクセスと非セキュア アクセスの分離が強制されます。

• 割り込みとタイマー

• 汎用割り込みコントローラ (GIC)

• 3 つのウォッチドッグ タイマー (WDT) (CPU ごとに 1 つとシステム WDT が 1 つ)

• 2 つのトリプル タイマー/カウンター (TTC)

• Cortex-A9 の CoreSight デバッグおよびトレースのサポート

• 命令およびトレース用のプログラム トレース マクロセル (PTM)

• ハードウェア ブレークポイントとトリガーを有効にするクロス トリガー インターフェイス (CTI)