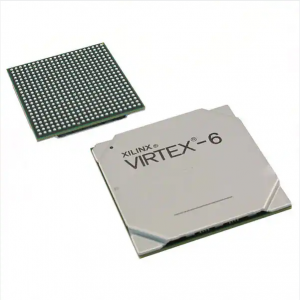

新しいオリジナルのXC6VLX240T-2FFG1759I集積回路

製品の属性

| タイプ | 説明 |

| カテゴリー | 集積回路 (IC) |

| 製造元 | AMDザイリンクス |

| シリーズ | Virtex®-6 LXT |

| パッケージ | トレイ |

| 製品の状態 | アクティブ |

| LAB/CLB の数 | 18840 |

| ロジックエレメント/セルの数 | 241152 |

| 合計RAMビット数 | 15335424 |

| I/O数 | 720 |

| 電圧 – 電源 | 0.95V~1.05V |

| 取付タイプ | 表面実装 |

| 動作温度 | -40℃~100℃(TJ) |

| パッケージ・ケース | 1759-BBGA、FCBGA |

| サプライヤーデバイスパッケージ | 1759-FCBGA (42.5×42.5) |

| 基本製品番号 | XC6VLX240 |

文書とメディア

| リソースの種類 | リンク |

| データシート | Virtex-6 FPGA データシート |

| 製品トレーニング モジュール | Virtex-6 FPGA の概要 |

| 環境情報 | ザイリンクス RoHS 認証 |

| PCNの設計・仕様 | 船舶間の鉛フリーに関する通知 31/Oct/2016 |

環境および輸出の分類

| 属性 | 説明 |

| RoHS ステータス | ROHS3準拠 |

| 感湿性レベル (MSL) | 4 (72時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

XC6VLX240T-2FFG1759I FPGA の概要

XC6VLX240T-2FFG1759I FPGA は、統合されたソフトウェアおよびハードウェア コンポーネントを提供するターゲット デザイン プラットフォーム用のプログラマブル シリコン基盤であり、設計者が開発サイクルの開始後すぐにイノベーションに集中できるようにします。第 3 世代 ASMBL (Advanced Silicon Modular Block) 列ベース アーキテクチャを使用するザイリンクス XC6VLX240T-2FFG1759I には、多くのシステム レベル ブロックが組み込まれています。これらの機能により、ロジック設計者は、FPGA ベースのシステムに最高レベルのパフォーマンスと機能を構築できます。40 nm の最先端の銅プロセス テクノロジーに基づいて構築された XC6VLX240T-2FFG1759I FPGA は、カスタム ASIC テクノロジーに代わるプログラム可能な代替品です。は、前例のないロジック、DSP、接続性、およびソフト マイクロプロセッサ機能を備えた、高性能ロジック設計者、高性能 DSP 設計者、および高性能組み込みシステム設計者のニーズに応える最適なソリューションを提供します。

ザイリンクス FPGA (フィールド プログラマブル ゲート アレイ) シリーズ XC6VLX240T-2FFG1759I は Virtex-6 LXT FPGA 720 I/O 1759FCBGA であり、FPGAkey.com で正規代理店から代替品および代替品、データシート、在庫、価格を確認できます。他のFPGA製品。

特徴

3 つのサブファミリー:

Virtex-6 LXT FPGA: 高度なシリアル接続を備えた高性能ロジック

Virtex-6 SXT FPGA: 高度なシリアル接続による最高の信号処理能力

Virtex-6 HXT FPGA: 最高帯域幅のシリアル接続

サブファミリー間の互換性

LXT デバイスと SXT デバイスは同じパッケージ内でフットプリントの互換性があります

高度な高性能 FPGA ロジック

リアル 6 入力ルックアップ テーブル (LUT) テクノロジー

デュアルLUT5(5入力LUT)オプション

豊富なレジスタミックスを必要とするアプリケーション向けの LUT/デュアル フリップフロップ ペア

ルーティング効率の向上

6 入力 LUT ごとに 64 ビット (または 2 つの 32 ビット) 分散 LUT RAM オプション

SRL32/デュアル SRL16 (登録出力オプション付き)

強力な混合モード クロック マネージャー (MMCM)

MMCM ブロックは、ゼロ遅延バッファリング、周波数合成、クロック位相シフト、入力ジッタ フィルタリング、および位相整合クロック分割を提供します。

36Kb ブロック RAM/FIFO

高性能並列 SelectIO テクノロジー

高度な DSP48E1 スライス

柔軟な構成オプション

SPIおよびパラレルフラッシュインターフェイス

専用のフォールバック再構成ロジックによるマルチビットストリームのサポート

自動バス幅検出

すべてのデバイスのシステム モニター機能

オンチップ/オフチップの熱および電源電圧の監視

監視されているすべての数量への JTAG アクセス

PCI Express 設計用の統合インターフェイス ブロック

GTX トランシーバー: 最大 6.6 Gb/s

480 Mb/s 未満のデータ レートは、FPGA ロジックのオーバーサンプリングによってサポートされます。

GTH トランシーバー: 2.488 Gb/s ~ 11 Gb/s 以上

統合された 10/100/1000 Mb/s イーサネット MAC ブロック

GTX トランシーバーを使用して 1000BASE-X PCS/PMA および SGMII をサポート

SelectIO テクノロジー リソースを使用して MII、GMII、および RGMII をサポート

2500Mb/秒のサポートが利用可能

40nm銅CMOSプロセス技術

1.0V コア電圧 (-1、-2、-3 スピード グレードのみ)

低電力 0.9V コア電圧オプション (-1L スピード グレードのみ)

信号整合性の高いフリップチップパッケージを標準パッケージまたは鉛フリーパッケージオプションで利用可能