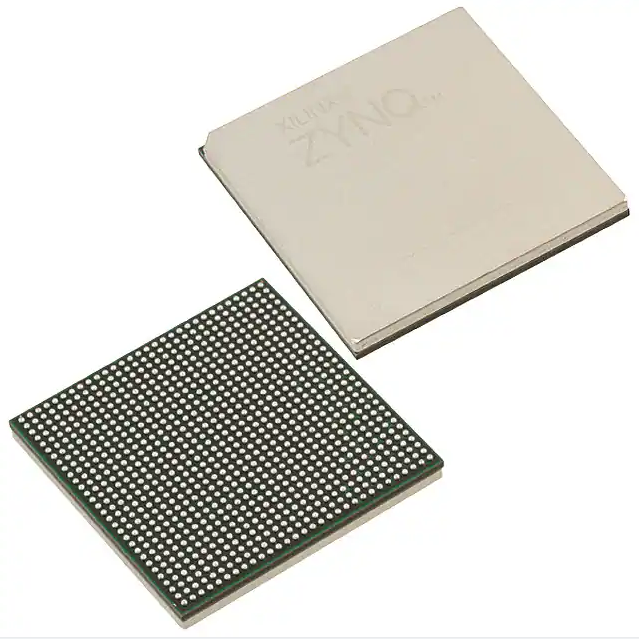

新しいオリジナルのXC5VFX30T-2FFG665I集積回路

製品の属性

| タイプ | 説明 | 選択する |

| カテゴリー | 集積回路 (IC) |

|

| 製造元 | AMDザイリンクス |

|

| シリーズ | Virtex®-5 FXT |

|

| パッケージ | トレイ |

|

| 製品の状態 | アクティブ |

|

| LAB/CLB の数 | 2560 |

|

| ロジックエレメント/セルの数 | 32768 |

|

| 合計RAMビット数 | 2506752 |

|

| I/O数 | 360 |

|

| 電圧 – 電源 | 0.95V~1.05V |

|

| 取付タイプ | 表面実装 |

|

| 動作温度 | -40℃~100℃(TJ) |

|

| パッケージ・ケース | 665-BBGA、FCBGA |

|

| サプライヤーデバイスパッケージ | 665-FCBGA (27×27) |

|

| 基本製品番号 | XC5VFX30 |

|

製品情報エラーを報告する

類似するものを見る

文書とメディア

| リソースの種類 | リンク |

| データシート | Virtex-5 ファミリの概要 |

| 環境情報 | ザイリンクス REACH211 証明書 |

| PCNの設計・仕様 | 船舶間の鉛フリーに関する通知 31/Oct/2016 |

環境および輸出の分類

| 属性 | 説明 |

| RoHS ステータス | ROHS3準拠 |

| 感湿性レベル (MSL) | 4 (72時間) |

| リーチステータス | REACHは影響を受けない |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

フィールド・プログラマブル・ゲート・アレイ

あフィールド・プログラマブル・ゲート・アレイ(FPGA) は集積回路製造後に顧客または設計者によって構成されるように設計されているため、この用語が生まれました。フィールドプログラマブル。FPGA 構成は通常、ハードウェア記述言語(HDL)、特定用途向け集積回路(ASIC)。回路図以前は構成を指定するために使用されていましたが、これは、電子設計の自動化ツール。

FPGA には次の配列が含まれていますプログラム可能な 論理ブロック、およびブロックを相互に配線できる再構成可能な相互接続の階層。ロジックブロックは複雑な処理を実行するように構成可能組み合わせ関数、または単純なように動作します論理ゲートのようにそしてそしてXOR。ほとんどの FPGA では、ロジック ブロックには次のものも含まれます。記憶要素、簡単かもしれませんビーチサンダルまたはより完全なメモリブロック。[1]多くの FPGA は再プログラムしてさまざまな機能を実装できます。論理関数、柔軟な対応が可能再構成可能なコンピューティングで行われたようにコンピューターソフトウェア.

FPGA は次の分野で重要な役割を果たしています。組み込みシステムこれは、ハードウェアと同時にシステム ソフトウェア開発を開始でき、開発の非常に早い段階でシステム パフォーマンス シミュレーションが可能になり、システム アーキテクチャを最終決定する前にさまざまなシステムの試行と設計の反復が可能になるためです。[2]

歴史[編集]

FPGA 産業は、プログラマブル読み取り専用メモリ(PROM) とプログラマブルロジックデバイス(PLD)。PROM と PLD にはどちらも、工場または現場でバッチでプログラムする (フィールド プログラマブル) オプションがありました。[3]

アルテラは 1983 年に設立され、1984 年に業界初の再プログラマブル ロジック デバイスである EP300 を納入しました。このデバイスは、パッケージに石英窓を備えており、ユーザーがダイに紫外線ランプを当ててデータを消去できるようになっていました。EPROMデバイス構成を保持するセル。[4]

ザイリンクス最初の商業的に実行可能なフィールドプログラマブルを生み出したゲートアレイ1985年に[3]– XC2064。[5]XC2064 にはプログラム可能なゲートとゲート間のプログラム可能な相互接続があり、これが新しい技術と市場の始まりでした。[6]XC2064 には、2 つの 3 入力を備えた 64 個の構成可能なロジック ブロック (CLB) がありました。ルックアップテーブル(LUT)。[7]

1987 年に、海軍水上戦センタースティーブ・カッセルマンが提案した、60万個の再プログラム可能なゲートを実装するコンピューターの開発実験に資金を提供した。カッセルマンは成功し、1992 年にシステムに関連する特許が発行されました。[3]

アルテラとザイリンクスは、競合他社の出現により、1985 年から 1990 年代半ばにかけて、揺るぎない成長を続け、市場シェアのかなりの部分を侵食しました。1993 年までに、アクテル (現在はマイクロセミ)は市場の約 18 パーセントを占めていました。[6]

1990 年代は、回路の洗練と生産量の両方において FPGA が急速に成長した時期でした。1990 年代初頭、FPGA は主に次の分野で使用されていました。電気通信そしてネットワーキング。10 年代の終わりまでに、FPGA は民生用、自動車用、産業用アプリケーションに導入されるようになりました。[8]

2013 年までに、Altera (31%)、Actel (10%)、Xilinx (36%) が合わせて FPGA 市場の約 77% を占めるようになりました。[9]

Microsoft のような企業は、高性能で計算集約型のシステム (データセンター彼らのBing 検索エンジン)、 によるワットあたりのパフォーマンスFPGA がもたらす利点。[10]Microsoft は FPGA の使用を開始しました。加速するBing は 2014 年に、2018 年に他のデータセンターのワークロード全体に FPGA を導入し始めました。アズール クラウドコンピューティングプラットホーム。[11]

次のタイムラインは、FPGA 設計のさまざまな側面における進捗状況を示しています。

ゲイツ

市場規模

- 1985: 最初の商用 FPGA : Xilinx XC2064[5][6]

- 1987年: 1,400万ドル[6]

- c.1993年: >3億8,500万ドル[6][検証に失敗しました]

- 2005年: 19億ドル[13]

- 2010 年の推定値: 27 億 5,000 万ドル[13]

- 2013年: 54億ドル[14]

- 2020 年の予測: 98 億ドル[14]

設計が始まります

あ設計開始は、FPGA に実装するための新しいカスタム デザインです。

デザイン[編集]

現在の FPGA には、次のような大量のリソースがあります。論理ゲートおよび RAM ブロックを使用して、複雑なデジタル計算を実装します。FPGA デザインでは非常に高速な I/O レートと双方向データが採用されているため、バス、セットアップ時間とホールド時間内で有効なデータの正しいタイミングを検証することが課題になります。

間取り図これにより、FPGA 内のリソース割り当てがこれらの時間制約を満たすことが可能になります。FPGA を使用すると、任意の論理関数を実装できます。ASIC実行できる。出荷後に機能をアップデートできること、部分的な再構成デザインの一部[17]また、ASIC 設計に比べて非経常エンジニアリング コストが低いため (一般に単価は高いにもかかわらず)、多くのアプリケーションに利点がもたらされます。[1]

一部の FPGA は、デジタル機能に加えてアナログ機能を備えています。最も一般的なアナログ機能はプログラム可能なものです。スルーレート各出力ピンで、エンジニアが負荷の軽いピンに低いレートを設定できるようにします。指輪またはカップルまた、高速チャネル上の負荷の高いピンに高いレートを設定すると、動作が遅くなりすぎます。[18][19]クォーツも一般的です水晶発振器、オンチップ抵抗容量発振器、およびフェーズロックループ埋め込まれたもの電圧制御発振器クロックの生成と管理、および高速シリアライザ/デシリアライザ (SERDES) 送信クロックと受信クロック リカバリに使用されます。かなり一般的なのは差動ですコンパレータに接続するように設計された入力ピン上差動信号チャンネル。いくつかの「混合信号FPGA」には周辺機器が統合されていますアナログデジタルコンバーター(ADC) およびデジタルアナログコンバーター(DAC) アナログ信号調整ブロックを使用して、DAC として動作できるようにします。システムオンチップ(SoC)。[20]このようなデバイスは、内部のプログラム可能な相互接続ファブリック上でデジタルの 1 と 0 を伝送する FPGA と、FPGA との間の境界線を曖昧にします。フィールドプログラマブルアナログアレイ(FPAA)、内部プログラマブル相互接続ファブリック上でアナログ値を伝送します。