XCVU9P-2FLGB2104I FPGA、VIRTEX ウルトラスケール、FCBGA-2104

商品情報

| TYPENo.ロジックブロックの数: | 2586150 |

| マクロセルの数: | 2586150マクロセル |

| FPGA ファミリ: | Virtex UltraScale シリーズ |

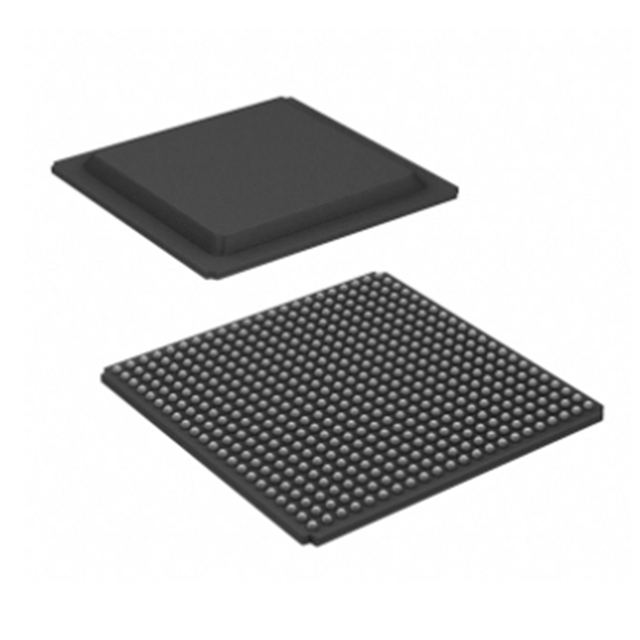

| ロジックケースのスタイル: | FCBGA |

| ピンの数: | 2104ピン |

| スピードグレードの数: | 2 |

| RAM ビットの合計: | 77722Kビット |

| I/O数: | 778I/O |

| クロック管理: | MMCM、PLL |

| 最小コア電源電圧: | 922mV |

| 最大コア電源電圧: | 979mV |

| I/O電源電圧: | 3.3V |

| 最大動作周波数: | 725MHz |

| 製品の範囲: | Virtex UltraScale XCVU9P |

| MSL: | - |

製品導入

BGAの略ですボール グリッド Q アレイ パッケージ。

BGA テクノロジーによってカプセル化されたメモリは、メモリ、BGA、TSOP の容量を変えることなく、メモリ容量を 3 倍に増やすことができます。

と比較して、体積が小さく、放熱性能と電気的性能が優れています。BGA パッケージング技術は平方インチあたりの記憶容量を大幅に向上させ、BGA パッケージング技術のメモリ製品を同じ容量で使用すると、体積は TSOP パッケージのわずか 3 分の 1 になります。さらに、伝統とともに

TSOP パッケージと比較して、BGA パッケージはより高速かつ効果的な熱放散方法を備えています。

集積回路技術の発展に伴い、集積回路のパッケージング要件はさらに厳しくなってきています。これは、パッケージング技術が製品の機能に関わるためであり、IC の周波数が 100MHz を超える場合、従来のパッケージング方法ではいわゆる「クロストーク・現象」が発生する可能性があり、IC のピン数が多い場合には、 208 ピンを超えると、従来のパッケージング方法には困難があるため、QFP パッケージングの使用に加えて、今日の高ピン数チップ (グラフィックス チップやチップセットなど) のほとんどは BGA(ボール グリッド アレイ) に切り替えられています。 PackageQ) パッケージング技術 BGA が登場すると、CPU やマザーボード上のサウス/ノース ブリッジ チップなどの高密度、高性能、マルチピン パッケージに最適な選択肢となりました。

BGA パッケージング技術は、次の 5 つのカテゴリに分類することもできます。

1.PBGA (Plasric BGA) 基板: 通常 2 ~ 4 層の有機材料で構成される多層基板。IntelシリーズCPU、Pentium 1l

Chuan IV プロセッサはすべてこの形式でパッケージ化されています。

2.CBGA (CeramicBCA) 基板: つまりセラミック基板。チップと基板間の電気接続は通常フリップチップです。

FlipChip(略してFC)のインストール方法。Intel シリーズ CPU、Pentium l、ll Pentium Pro プロセッサーを使用

カプセル化の一種。

3.FCBGA(FilpChipBGA) 基板: 硬質多層基板。

4.TBGA (TapeBGA) 基板: 基板はリボンソフト 1-2 層 PCB 回路基板です。

5.CDPBGA (Carty Down PBGA) 基板: パッケージの中央にある低い正方形のチップ領域 (キャビティ領域とも呼ばれます) を指します。

BGA パッケージには次の機能があります。

1).10 ピン数は増えますが、ピン間の距離が QFP パッケージに比べて大きくなるため、歩留まりが向上します。

2).BGAの消費電力は増加しますが、制御コラプスチップ溶接方式により通電加熱性能を向上させることができます。

3)。信号伝送遅延が小さく、適応周波数が大幅に向上します。

4)。アセンブリはコプレーナ溶接できるため、信頼性が大幅に向上します。